#### A Novel 8T TFET-MOSFET Hybrid SRAM Cell For PEKING UNIVERSITY A Novel 8T TFET-MOSFET Hybrid SRAM Cell For Ultra-Low Power And Computing In-memory Applications

Yingxi Zhou<sup>1</sup>, Rundong Jia<sup>2\*</sup>, Rong Zhao<sup>3</sup>, Kaifeng Wang<sup>2</sup>, Qianqian Huang<sup>2,4\*</sup> and Ru Huang<sup>2,4\*</sup> <sup>1</sup>School of Software & Microelectronic, Peking University, Beijing 102600, China; <sup>2</sup>School of Integrated Circuits, Peking University, Beijing 100871, China; <sup>3</sup>School of Integrated Circuits, Anhui University, Hefei 230601, China; <sup>4</sup>Beijing Advanced Innovation Center for Integrated Circuits, Beijing 100871, China.

\*E-mail: jiard@pku.edu.cn; hqq@pku.edu.cn; ruhuang@pku.edu.cn

### ABSTRACT

In this work, a novel 8T Tunnel FET (TFET)-MOSFET hybrid SRAM design with awareness of the impacts of large gate-drain capacitance in TFET is proposed and simulated. The proposed design utilizes MOSFET and TFET as upper and down transistor respectively in the read path, which can avoid the voltage coupling in conventional cascade TFET structure. Compared with conventional 6T CMOS SRAM, it achieves significant reduction in static and operation power, as well as improved static noise margin (SNM), leading to the lowest read power-delay-product (PDP). Moreover, its application for multiply-and-accumulate (MAC) operations in analog computing in-memory (CIM) is also demonstrated with high energy efficiency showing its great potential for energy-efficient AIoT applications.

## INTRODUCTION

- > Unique Electrical Characteristics of TFETs

- **Unidirectional conduction**

# **RESULTS & DISCUSSION**

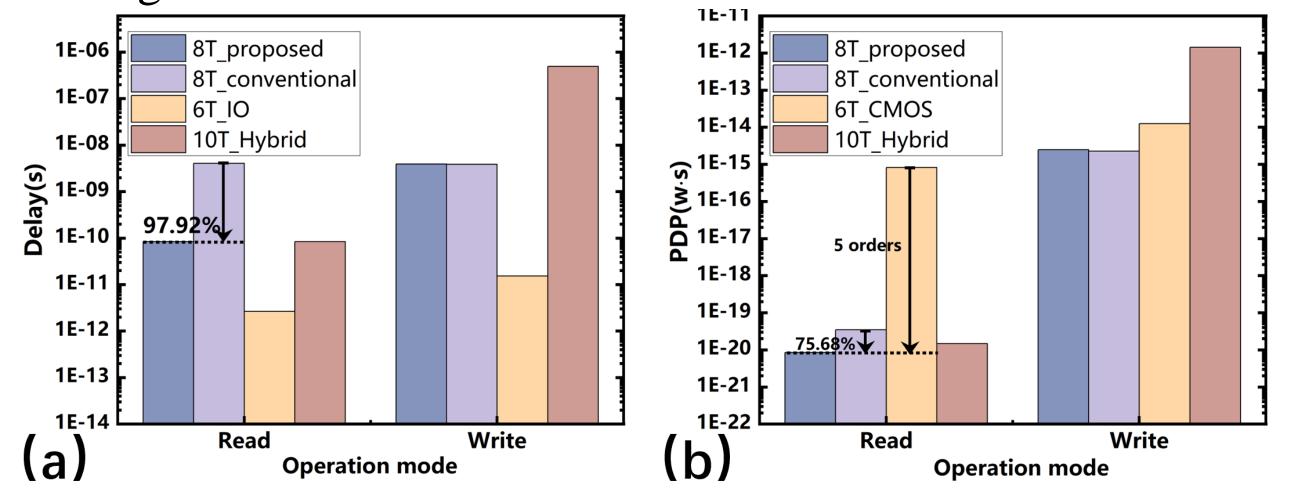

- Comparison for different SRAM topologies:

- Delay

- Read delay is reduced by 97.92% compared with conventional 8T due to voltage coupling from node x to gate of Tn3, read delay is larger than 6T CMOS SRAM.

- Write delay is the same as conventional 8T but higher than 6T CMOS SRAM.

- PDP

- Read PDP is 75.68% lower than the conventional 8T and 5 orders of magnitude lower than the 6T CMOS SRAM.

- Write PDP is similar to the conventional 8T and 1 order of magnitude lower than the 6T CMOS SRAM.

- Forward p-i-n current (I<sub>PIN</sub>)

- These two may lead to functional errors or increased power consumption, and have been considered in previous studies.

- Large gate-drain capacitance (C<sub>GD</sub>)

- This will cause delay issue and has rarely been considered.

- A new 8T TFET-MOSFET hybrid SRAM cell design with consideration of  $C_{GD}$  for better PDP has been proposed and application in CIM is demonstrated.

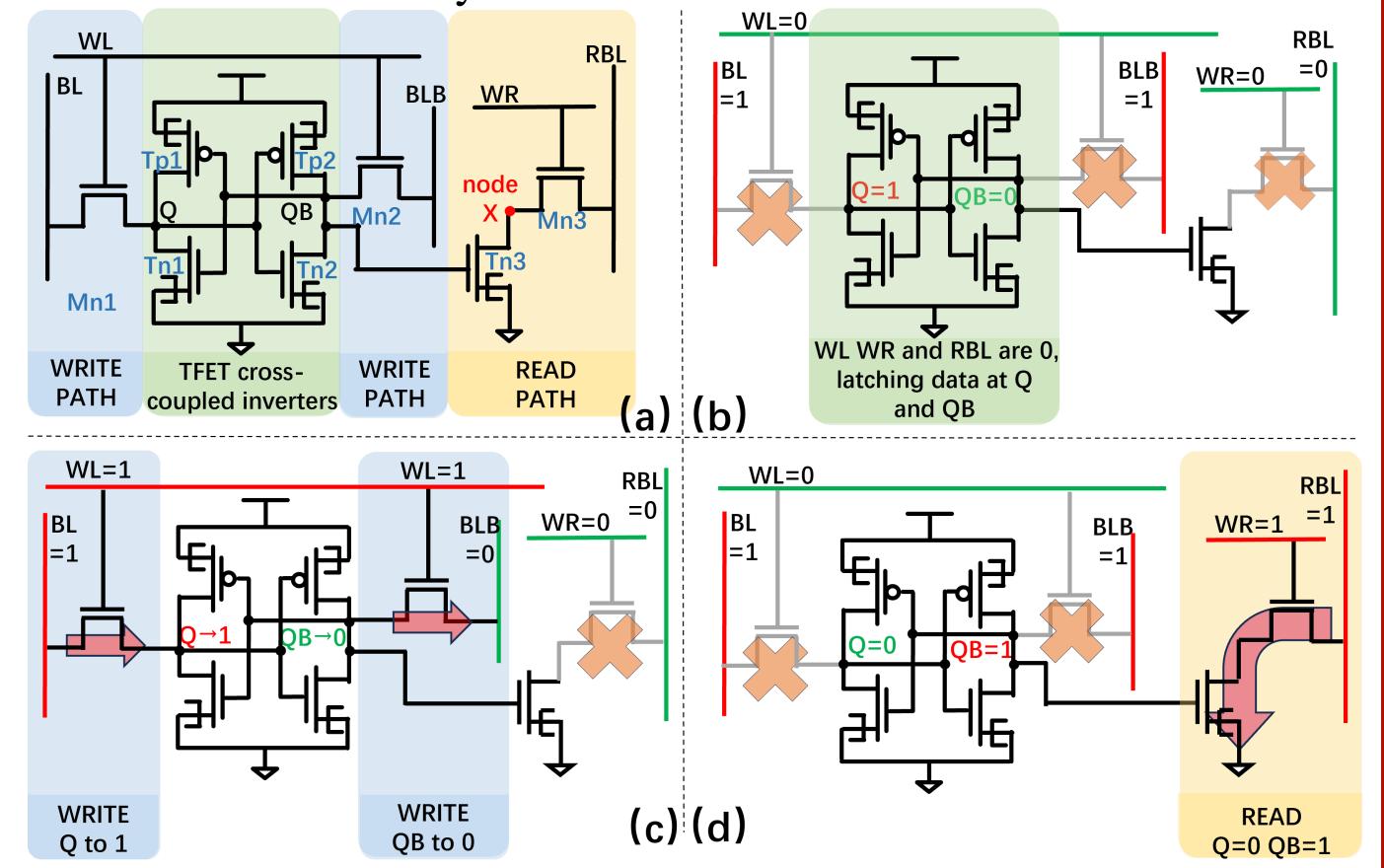

## **DESIGN OF 8T HYBRID SRAM CELL**

- > The design employs a cross-coupled inverter structure.

- > Write path: MOSFETs as dual-ended access transistors.

- Read path: a series connection of a MOSFET and a TFET, with the TFET's drain connected to RBL through a MOSFET and its source connected to ground.

- Pulse on WR can be coupled to RBL through  $C_{GD}$

- Smaller  $C_{GD}$  in MOS  $\rightarrow$  smaller signal spikes in  $V_{RBL} \rightarrow$  smaller read delay

Fig 2 : benchmark of different SRAM topologies.

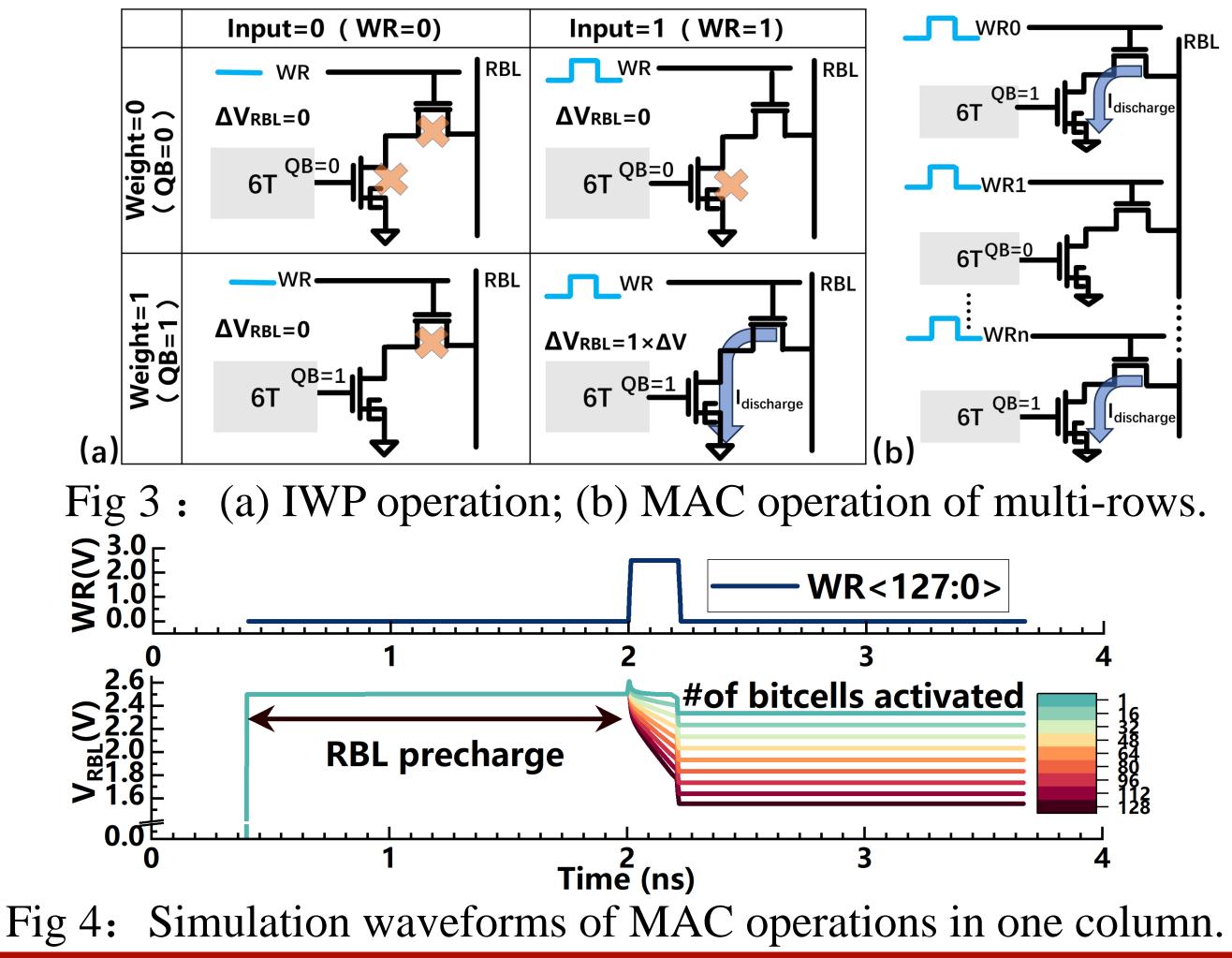

#### > CIM Application:

- When multiple rows of WRs are activated, each bitcell performs an input-weight product (IWP) operation, and the result will multiply by column on RBL.

- The MAC results exhibit good linearity.

Fig 1: (a) Proposed 8T design & Operations (b) Hold (c) Write (d) Read.

#### SUMMARY

This work presents a novel 8T TFET-MOSFET hybrid SRAM showing considerably power and PDP reduction compared with 6T CMOS SRAM and other reported TFET SRAM designs respectively. Additionally, MAC operation can be realized utilizing the proposed SRAM with higher energy efficiency of one order of magnitude than that of 6T CMOS SRAM array. The result shows the great potential of TFET SRAM in ultra-low power application.